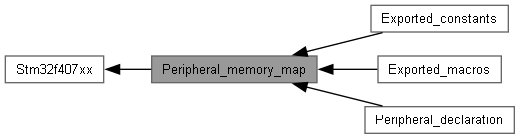

Collaboration diagram for Peripheral_memory_map:

Collaboration diagram for Peripheral_memory_map:Topics | |

| Peripheral_declaration | |

| Exported_constants | |

| Exported_macros | |

Data Structures | |

| struct | _memory |

Typedefs | |

| typedef struct _memory | MCU_MemoryTypeDef |

Variables | |

| MCU_MemoryTypeDef | MCU_MEM |

| DBGMCU_TypeDef | DEBUG_MCU |

Detailed Description

Macro Definition Documentation

◆ FLASH_BASE_SHIFT

| #define FLASH_BASE_SHIFT 0x08000000UL |

FLASH(up to 1 MB) base address in the alias region

◆ FLASH_END_SHIFT

| #define FLASH_END_SHIFT 0x080FFFFFUL |

FLASH end address

◆ CCMDATARAM_BASE_SHIFT

| #define CCMDATARAM_BASE_SHIFT 0x10000000UL |

CCM(core coupled memory) data RAM(64 KB) base address in the alias region

◆ CCMDATARAM_END_SHIFT

| #define CCMDATARAM_END_SHIFT 0x1000FFFFUL |

CCM data RAM end address

◆ FLASH_OTP_BASE_SHIFT

| #define FLASH_OTP_BASE_SHIFT 0x1FFF7800UL |

Base address of : (up to 528 Bytes) embedded FLASH OTP Area

◆ FLASH_OTP_END_SHIFT

| #define FLASH_OTP_END_SHIFT 0x1FFF7A0FUL |

End address of : (up to 528 Bytes) embedded FLASH OTP Area

◆ SRAM1_BASE_SHIFT

| #define SRAM1_BASE_SHIFT 0x20000000UL |

SRAM1(112 KB) base address in the alias region

◆ SRAM2_BASE_SHIFT

| #define SRAM2_BASE_SHIFT 0x2001C000UL |

SRAM2(16 KB) base address in the alias region

◆ SRAM1_BB_BASE_SHIFT

| #define SRAM1_BB_BASE_SHIFT 0x22000000UL |

SRAM1(112 KB) base address in the bit-band region

◆ SRAM2_BB_BASE_SHIFT

| #define SRAM2_BB_BASE_SHIFT 0x22380000UL |

SRAM2(16 KB) base address in the bit-band region

◆ PERIPH_BASE_SHIFT

| #define PERIPH_BASE_SHIFT 0x40000000UL |

Peripheral base address in the alias region

◆ BKPSRAM_BASE_SHIFT

| #define BKPSRAM_BASE_SHIFT 0x40024000UL |

Backup SRAM(4 KB) base address in the alias region

◆ PERIPH_BB_BASE_SHIFT

| #define PERIPH_BB_BASE_SHIFT 0x42000000UL |

Peripheral base address in the bit-band region

◆ BKPSRAM_BB_BASE_SHIFT

| #define BKPSRAM_BB_BASE_SHIFT 0x42480000UL |

Backup SRAM(4 KB) base address in the bit-band region

◆ FSMC_R_BASE_SHIFT

| #define FSMC_R_BASE_SHIFT 0xA0000000UL |

FSMC registers base address

◆ MCU_MEM_END

| #define MCU_MEM_END 0xA0000FFFUL |

CCM data RAM end address

◆ CCMDATARAM_SIZE

| #define CCMDATARAM_SIZE 0x10000UL /* (64 KB) */ |

◆ SRAM1_SIZE

| #define SRAM1_SIZE 0x1C000UL /* (112 KB) */ |

◆ SRAM2_SIZE

| #define SRAM2_SIZE 0x4000UL /* (16 KB) */ |

◆ BKPSRAM_SIZE

| #define BKPSRAM_SIZE 0x1000UL /* (4 KB) */ |

◆ FLASH_SIZE

| #define FLASH_SIZE (CCMDATARAM_BASE_SHIFT - FLASH_BASE_SHIFT) |

◆ FLASH_OTP_SIZE

| #define FLASH_OTP_SIZE (SRAM1_BASE_SHIFT - FLASH_OTP_BASE_SHIFT) |

◆ SRAM1_BB_SIZE

| #define SRAM1_BB_SIZE (SRAM2_BB_BASE_SHIFT - SRAM1_BB_BASE_SHIFT) |

◆ SRAM2_BB_SIZE

| #define SRAM2_BB_SIZE (PERIPH_BASE_SHIFT - SRAM2_BB_BASE_SHIFT) |

◆ PERIPH_SIZE

| #define PERIPH_SIZE (BKPSRAM_BASE_SHIFT - PERIPH_BASE_SHIFT) |

◆ PERIPH_BB_SIZE

| #define PERIPH_BB_SIZE (BKPSRAM_BB_BASE_SHIFT - PERIPH_BB_BASE_SHIFT) |

◆ FSMC_R_SIZE

| #define FSMC_R_SIZE (MCU_MEM_END - FSMC_R_BASE_SHIFT) |

◆ FLASH_BASE

| #define FLASH_BASE (MCU_MEM.CCMDATARAM_BASE) |

FLASH(up to 1 MB) base address in the alias region

◆ CCMDATARAM_BASE

| #define CCMDATARAM_BASE (MCU_MEM.CCMDATARAM_BASE) |

CCM(core coupled memory) data RAM(64 KB) base address in the alias region

◆ SRAM1_BASE

| #define SRAM1_BASE (MCU_MEM.SRAM1_BASE) |

SRAM1(112 KB) base address in the alias region

◆ SRAM2_BASE

| #define SRAM2_BASE (MCU_MEM.SRAM2_BASE) |

SRAM2(16 KB) base address in the alias region

◆ PERIPH_BASE

| #define PERIPH_BASE (MCU_MEM.PERIPH_BASE) |

Peripheral base address in the alias region

◆ BKPSRAM_BASE

| #define BKPSRAM_BASE (MCU_MEM.BKPSRAM_BASE) |

Backup SRAM(4 KB) base address in the alias region

◆ FSMC_R_BASE

| #define FSMC_R_BASE (MCU_MEM.FSMC_R_BASE) |

FSMC registers base address

◆ SRAM1_BB_BASE

| #define SRAM1_BB_BASE (MCU_MEM.SRAM1_BB_BASE) |

SRAM1(112 KB) base address in the bit-band region

◆ SRAM2_BB_BASE

| #define SRAM2_BB_BASE (MCU_MEM.SRAM2_BB_BASE) |

SRAM2(16 KB) base address in the bit-band region

◆ PERIPH_BB_BASE

| #define PERIPH_BB_BASE (MCU_MEM.PERIPH_BB_BASE) |

Peripheral base address in the bit-band region

◆ BKPSRAM_BB_BASE

| #define BKPSRAM_BB_BASE (MCU_MEM.BKPSRAM_BB_BASE) |

Backup SRAM(4 KB) base address in the bit-band region

◆ FLASH_END

| #define FLASH_END (MCU_MEM.FLASH_END) |

FLASH end address

◆ FLASH_OTP_BASE

| #define FLASH_OTP_BASE (MCU_MEM.FLASH_OTP_BASE) |

Base address of : (up to 528 Bytes) embedded FLASH OTP Area

◆ FLASH_OTP_END

| #define FLASH_OTP_END (MCU_MEM.FLASH_OTP_END) |

End address of : (up to 528 Bytes) embedded FLASH OTP Area

◆ CCMDATARAM_END

| #define CCMDATARAM_END (MCU_MEM.CCMDATARAM_END) |

CCM data RAM end address

◆ SRAM_BASE

| #define SRAM_BASE SRAM1_BASE |

◆ SRAM_BB_BASE

| #define SRAM_BB_BASE SRAM1_BB_BASE |

Peripheral memory map

◆ APB1PERIPH_BASE

| #define APB1PERIPH_BASE PERIPH_BASE |

◆ APB2PERIPH_BASE

| #define APB2PERIPH_BASE (PERIPH_BASE + 0x00010000UL) |

◆ AHB1PERIPH_BASE

| #define AHB1PERIPH_BASE (PERIPH_BASE + 0x00020000UL) |

◆ AHB2PERIPH_BASE

| #define AHB2PERIPH_BASE (PERIPH_BASE + 0x10000000UL) |

APB1 peripherals

◆ TIM2_BASE

| #define TIM2_BASE (APB1PERIPH_BASE + 0x0000UL) |

◆ TIM3_BASE

| #define TIM3_BASE (APB1PERIPH_BASE + 0x0400UL) |

◆ TIM4_BASE

| #define TIM4_BASE (APB1PERIPH_BASE + 0x0800UL) |

◆ TIM5_BASE

| #define TIM5_BASE (APB1PERIPH_BASE + 0x0C00UL) |

◆ TIM6_BASE

| #define TIM6_BASE (APB1PERIPH_BASE + 0x1000UL) |

◆ TIM7_BASE

| #define TIM7_BASE (APB1PERIPH_BASE + 0x1400UL) |

◆ TIM12_BASE

| #define TIM12_BASE (APB1PERIPH_BASE + 0x1800UL) |

◆ TIM13_BASE

| #define TIM13_BASE (APB1PERIPH_BASE + 0x1C00UL) |

◆ TIM14_BASE

| #define TIM14_BASE (APB1PERIPH_BASE + 0x2000UL) |

◆ RTC_BASE

| #define RTC_BASE (APB1PERIPH_BASE + 0x2800UL) |

◆ WWDG_BASE

| #define WWDG_BASE (APB1PERIPH_BASE + 0x2C00UL) |

◆ IWDG_BASE

| #define IWDG_BASE (APB1PERIPH_BASE + 0x3000UL) |

◆ I2S2ext_BASE

| #define I2S2ext_BASE (APB1PERIPH_BASE + 0x3400UL) |

◆ SPI2_BASE

| #define SPI2_BASE (APB1PERIPH_BASE + 0x3800UL) |

◆ SPI3_BASE

| #define SPI3_BASE (APB1PERIPH_BASE + 0x3C00UL) |

◆ I2S3ext_BASE

| #define I2S3ext_BASE (APB1PERIPH_BASE + 0x4000UL) |

◆ USART2_BASE

| #define USART2_BASE (APB1PERIPH_BASE + 0x4400UL) |

◆ USART3_BASE

| #define USART3_BASE (APB1PERIPH_BASE + 0x4800UL) |

◆ UART4_BASE

| #define UART4_BASE (APB1PERIPH_BASE + 0x4C00UL) |

◆ UART5_BASE

| #define UART5_BASE (APB1PERIPH_BASE + 0x5000UL) |

◆ I2C1_BASE

| #define I2C1_BASE (APB1PERIPH_BASE + 0x5400UL) |

◆ I2C2_BASE

| #define I2C2_BASE (APB1PERIPH_BASE + 0x5800UL) |

◆ I2C3_BASE

| #define I2C3_BASE (APB1PERIPH_BASE + 0x5C00UL) |

◆ CAN1_BASE

| #define CAN1_BASE (APB1PERIPH_BASE + 0x6400UL) |

◆ CAN2_BASE

| #define CAN2_BASE (APB1PERIPH_BASE + 0x6800UL) |

◆ PWR_BASE

| #define PWR_BASE (APB1PERIPH_BASE + 0x7000UL) |

◆ DAC_BASE

| #define DAC_BASE (APB1PERIPH_BASE + 0x7400UL) |

APB2 peripherals

◆ TIM1_BASE

| #define TIM1_BASE (APB2PERIPH_BASE + 0x0000UL) |

◆ TIM8_BASE

| #define TIM8_BASE (APB2PERIPH_BASE + 0x0400UL) |

◆ USART1_BASE

| #define USART1_BASE (APB2PERIPH_BASE + 0x1000UL) |

◆ USART6_BASE

| #define USART6_BASE (APB2PERIPH_BASE + 0x1400UL) |

◆ ADC1_BASE

| #define ADC1_BASE (APB2PERIPH_BASE + 0x2000UL) |

◆ ADC2_BASE

| #define ADC2_BASE (APB2PERIPH_BASE + 0x2100UL) |

◆ ADC3_BASE

| #define ADC3_BASE (APB2PERIPH_BASE + 0x2200UL) |

◆ ADC123_COMMON_BASE

| #define ADC123_COMMON_BASE (APB2PERIPH_BASE + 0x2300UL) |

◆ ADC_BASE

| #define ADC_BASE ADC123_COMMON_BASE |

◆ SDIO_BASE

| #define SDIO_BASE (APB2PERIPH_BASE + 0x2C00UL) |

◆ SPI1_BASE

| #define SPI1_BASE (APB2PERIPH_BASE + 0x3000UL) |

◆ SYSCFG_BASE

| #define SYSCFG_BASE (APB2PERIPH_BASE + 0x3800UL) |

◆ EXTI_BASE

| #define EXTI_BASE (APB2PERIPH_BASE + 0x3C00UL) |

◆ TIM9_BASE

| #define TIM9_BASE (APB2PERIPH_BASE + 0x4000UL) |

◆ TIM10_BASE

| #define TIM10_BASE (APB2PERIPH_BASE + 0x4400UL) |

◆ TIM11_BASE

| #define TIM11_BASE (APB2PERIPH_BASE + 0x4800UL) |

AHB1 peripherals

◆ GPIOA_BASE

| #define GPIOA_BASE (AHB1PERIPH_BASE + 0x0000UL) |

◆ GPIOB_BASE

| #define GPIOB_BASE (AHB1PERIPH_BASE + 0x0400UL) |

◆ GPIOC_BASE

| #define GPIOC_BASE (AHB1PERIPH_BASE + 0x0800UL) |

◆ GPIOD_BASE

| #define GPIOD_BASE (AHB1PERIPH_BASE + 0x0C00UL) |

◆ GPIOE_BASE

| #define GPIOE_BASE (AHB1PERIPH_BASE + 0x1000UL) |

◆ GPIOF_BASE

| #define GPIOF_BASE (AHB1PERIPH_BASE + 0x1400UL) |

◆ GPIOG_BASE

| #define GPIOG_BASE (AHB1PERIPH_BASE + 0x1800UL) |

◆ GPIOH_BASE

| #define GPIOH_BASE (AHB1PERIPH_BASE + 0x1C00UL) |

◆ GPIOI_BASE

| #define GPIOI_BASE (AHB1PERIPH_BASE + 0x2000UL) |

◆ CRC_BASE

| #define CRC_BASE (AHB1PERIPH_BASE + 0x3000UL) |

◆ RCC_BASE

| #define RCC_BASE (AHB1PERIPH_BASE + 0x3800UL) |

◆ FLASH_R_BASE

| #define FLASH_R_BASE (AHB1PERIPH_BASE + 0x3C00UL) |

◆ DMA1_BASE

| #define DMA1_BASE (AHB1PERIPH_BASE + 0x6000UL) |

◆ DMA1_Stream0_BASE

| #define DMA1_Stream0_BASE (DMA1_BASE + 0x010UL) |

◆ DMA1_Stream1_BASE

| #define DMA1_Stream1_BASE (DMA1_BASE + 0x028UL) |

◆ DMA1_Stream2_BASE

| #define DMA1_Stream2_BASE (DMA1_BASE + 0x040UL) |

◆ DMA1_Stream3_BASE

| #define DMA1_Stream3_BASE (DMA1_BASE + 0x058UL) |

◆ DMA1_Stream4_BASE

| #define DMA1_Stream4_BASE (DMA1_BASE + 0x070UL) |

◆ DMA1_Stream5_BASE

| #define DMA1_Stream5_BASE (DMA1_BASE + 0x088UL) |

◆ DMA1_Stream6_BASE

| #define DMA1_Stream6_BASE (DMA1_BASE + 0x0A0UL) |

◆ DMA1_Stream7_BASE

| #define DMA1_Stream7_BASE (DMA1_BASE + 0x0B8UL) |

◆ DMA2_BASE

| #define DMA2_BASE (AHB1PERIPH_BASE + 0x6400UL) |

◆ DMA2_Stream0_BASE

| #define DMA2_Stream0_BASE (DMA2_BASE + 0x010UL) |

◆ DMA2_Stream1_BASE

| #define DMA2_Stream1_BASE (DMA2_BASE + 0x028UL) |

◆ DMA2_Stream2_BASE

| #define DMA2_Stream2_BASE (DMA2_BASE + 0x040UL) |

◆ DMA2_Stream3_BASE

| #define DMA2_Stream3_BASE (DMA2_BASE + 0x058UL) |

◆ DMA2_Stream4_BASE

| #define DMA2_Stream4_BASE (DMA2_BASE + 0x070UL) |

◆ DMA2_Stream5_BASE

| #define DMA2_Stream5_BASE (DMA2_BASE + 0x088UL) |

◆ DMA2_Stream6_BASE

| #define DMA2_Stream6_BASE (DMA2_BASE + 0x0A0UL) |

◆ DMA2_Stream7_BASE

| #define DMA2_Stream7_BASE (DMA2_BASE + 0x0B8UL) |

◆ ETH_BASE

| #define ETH_BASE (AHB1PERIPH_BASE + 0x8000UL) |

◆ ETH_MAC_BASE

| #define ETH_MAC_BASE (ETH_BASE) |

◆ ETH_MMC_BASE

| #define ETH_MMC_BASE (ETH_BASE + 0x0100UL) |

◆ ETH_PTP_BASE

| #define ETH_PTP_BASE (ETH_BASE + 0x0700UL) |

◆ ETH_DMA_BASE

| #define ETH_DMA_BASE (ETH_BASE + 0x1000UL) |

AHB2 peripherals

◆ DCMI_BASE

| #define DCMI_BASE (AHB2PERIPH_BASE + 0x50000UL) |

◆ RNG_BASE

| #define RNG_BASE (AHB2PERIPH_BASE + 0x60800UL) |

FSMC Bankx registers base address

◆ FSMC_Bank1_R_BASE

| #define FSMC_Bank1_R_BASE (FSMC_R_BASE + 0x0000UL) |

◆ FSMC_Bank1E_R_BASE

| #define FSMC_Bank1E_R_BASE (FSMC_R_BASE + 0x0104UL) |

◆ FSMC_Bank2_3_R_BASE

| #define FSMC_Bank2_3_R_BASE (FSMC_R_BASE + 0x0060UL) |

◆ FSMC_Bank4_R_BASE

| #define FSMC_Bank4_R_BASE (FSMC_R_BASE + 0x00A0UL) |

Debug MCU registers base address

◆ DBGMCU_BASE

| #define DBGMCU_BASE (&DEBUG_MCU) |

USB registers base address

◆ USB_OTG_HS_PERIPH_BASE

| #define USB_OTG_HS_PERIPH_BASE 0x40040000UL |

◆ USB_OTG_FS_PERIPH_BASE

| #define USB_OTG_FS_PERIPH_BASE 0x50000000UL |

◆ USB_OTG_GLOBAL_BASE

| #define USB_OTG_GLOBAL_BASE 0x000UL |

◆ USB_OTG_DEVICE_BASE

| #define USB_OTG_DEVICE_BASE 0x800UL |

◆ USB_OTG_IN_ENDPOINT_BASE

| #define USB_OTG_IN_ENDPOINT_BASE 0x900UL |

◆ USB_OTG_OUT_ENDPOINT_BASE

| #define USB_OTG_OUT_ENDPOINT_BASE 0xB00UL |

◆ USB_OTG_EP_REG_SIZE

| #define USB_OTG_EP_REG_SIZE 0x20UL |

◆ USB_OTG_HOST_BASE

| #define USB_OTG_HOST_BASE 0x400UL |

◆ USB_OTG_HOST_PORT_BASE

| #define USB_OTG_HOST_PORT_BASE 0x440UL |

◆ USB_OTG_HOST_CHANNEL_BASE

| #define USB_OTG_HOST_CHANNEL_BASE 0x500UL |

◆ USB_OTG_HOST_CHANNEL_SIZE

| #define USB_OTG_HOST_CHANNEL_SIZE 0x20UL |

◆ USB_OTG_PCGCCTL_BASE

| #define USB_OTG_PCGCCTL_BASE 0xE00UL |

◆ USB_OTG_FIFO_BASE

| #define USB_OTG_FIFO_BASE 0x1000UL |

◆ USB_OTG_FIFO_SIZE

| #define USB_OTG_FIFO_SIZE 0x1000UL |

◆ UID_BASE

| #define UID_BASE 0x1FFF7A10UL |

Unique device ID register base address

◆ FLASHSIZE_BASE

| #define FLASHSIZE_BASE 0x1FFF7A22UL |

FLASH Size register base address

◆ PACKAGE_BASE

| #define PACKAGE_BASE 0x1FFF7BF0UL |

Package size register base address

Typedef Documentation

◆ MCU_MemoryTypeDef

| typedef struct _memory MCU_MemoryTypeDef |

Variable Documentation

◆ MCU_MEM

|

extern |

◆ DEBUG_MCU

| DBGMCU_TypeDef DEBUG_MCU |